#### **Features and Benefits**

- AEC Q100 Grade 0 Automotive Qualified

- Constant current LED drive

- 5 to 50 V supply

- Boost mode

- Drives up to 15 LEDs in series

- Programmable switching frequency 100 to 700 kHz

- Open LED overvoltage indication and protection

- Single and multiple LED short indication

- LED short to ground and supply protection

- PWM dimming control

#### **Applications:**

- Automotive high power LED lighting systems

- Fog lights, reversing lights, daytime running lights

- Headlights

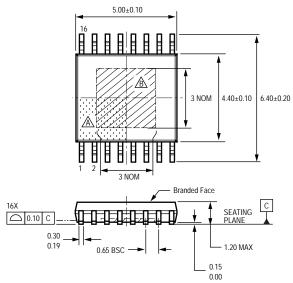

# Package: 16-pin TSSOP with exposed thermal pad (suffix LP)

Not to scale

#### Description

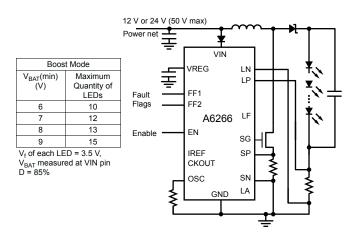

The A6266 is a boost converter controller, providing a programmable constant current output for driving high power LEDs in series. Driving the LEDs in series ensures identical currents and uniform brightness. For automotive applications, optimum performance is achieved when driving up to 15 LEDs at currents up to 1 A.

The A6266 provides a cost-effective solution using an external logic-level MOSFET and minimum additional external components. The maximum LED current is set with a single external sense resistor and can be modified using a current reference input. Direct PWM control is possible via the Enable input, which also provides a shutdown mode.

Integrated diagnostics and two fault outputs give indication of undervoltage, chip overtemperature, output open circuit, LED short circuit and LED undercurrent, and can be configured to provide short to supply and short to ground protection for the LED connections. A unique feature is the ability to detect one or more shorted LEDs.

The device is provided in a 16-pin TSSOP package with exposed thermal pad (suffix LP). It is lead (Pb) free, with 100% matte tin leadframe plating.

### **Typical Application Diagram**

| Selection Guide |                             |                                       |  |  |  |  |  |

|-----------------|-----------------------------|---------------------------------------|--|--|--|--|--|

| Part Number     | Packing                     | Package                               |  |  |  |  |  |

| A6266KLPTR-T    | 4000 pieces per 13-in. reel | 16-pin TSSOP with exposed thermal pad |  |  |  |  |  |

#### Characteristic Symbol Notes Rating Unit Load Supply Voltage $V_{IN}$ -0.3 to 50 V Pins FF1, EN -0.3 to 50 V Pins FF2, CKOUT -0.3 to 6.5 V Pin OSC -0.3 to 6.5 V Pin SG -0.3 to 6.5 V Pins LA, LN -0.3 to 7 V Pin LF With respect to LA -6 to 6 V Pin LP With respect to LN -6 to 6 V Pin SP, SN -0.3 to 5 V Pin VREG V -0.3 to 7 Pin THTH V -0.3 to 7 Pin IREF V -0.3 to 7 Junction Temperature T<sub>J</sub>(max) 150 °C Storage Temperature Range -55 to 150 °C T<sub>stg</sub> **Operating Temperature Range** $\mathsf{T}_\mathsf{A}$ Range K -40 to 150 °C

#### **Absolute Maximum Ratings** With respect to GND at T<sub>A</sub> = 25°C, unless otherwise specified

Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic                                                                   | Symbol           | Test Conditions*                                                  | Value | Unit |

|----------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------|-------|------|

| Package Thermal Resistance                                                       | R <sub>θJA</sub> | On 4-layer PCB based on JEDEC standard                            | 34    | °C/W |

| (Junction to Ambient)                                                            | κ <sub>θJA</sub> | On 2-layer PCB with 3.8 in. <sup>2</sup> of copper area each side | 43    | °C/W |

| Package Thermal Resistance<br>(Junction to Exposed Pad)         R <sub>θJP</sub> |                  |                                                                   | 2     | °C/W |

\*Additional thermal information available on the Allegro website

2

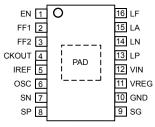

#### **Pin-out Diagram**

#### **Terminal List Table**

| Number | Name  | Function                            |  |

|--------|-------|-------------------------------------|--|

| 1      | EN    | Enable chip                         |  |

| 2      | FF1   | Fault flag                          |  |

| 3      | FF2   | Fault flag                          |  |

| 4      | CKOUT | Oscillator output, with phase shift |  |

| 5      | IREF  | Current reference                   |  |

| 6      | OSC   | Oscillator input/frequency set      |  |

| 7      | SN    | Switch current sense -ve input      |  |

| 8      | SP    | Switch current sense +ve input      |  |

| 9      | SG    | Switch gate drive                   |  |

| 10     | GND   | Ground                              |  |

| 11     | VREG  | Internal regulator capacitor        |  |

| 12     | VIN   | Main supply                         |  |

| 13     | LP    | Load current sense +ve input        |  |

| 14     | LN    | Load current sense -ve input        |  |

| 15     | LA    | LED string voltage sense            |  |

| 16     | LF    | Reference LED voltage sense         |  |

| _      | PAD   | Exposed thermal pad                 |  |

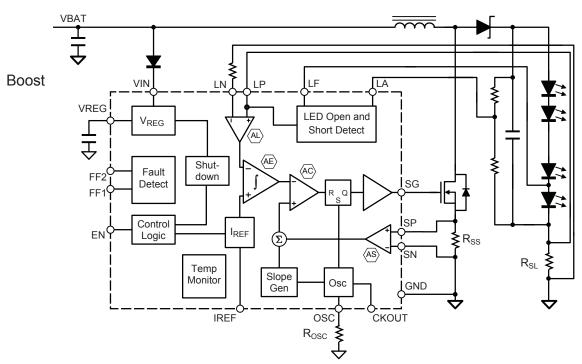

#### **Functional Block Diagram**

#### **ELECTRICAL CHARACTERISTICS**<sup>1</sup> Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{IN} = 6$ to 40 V; unless otherwise noted

| Characteristics Symbol                                  |                       | Test Conditions                                    | Min.                      | Тур. | Max.             | Unit |

|---------------------------------------------------------|-----------------------|----------------------------------------------------|---------------------------|------|------------------|------|

| Supply and Reference                                    |                       |                                                    | '                         |      |                  |      |

| V <sub>IN</sub> Functional Operating Range <sup>2</sup> |                       |                                                    | 5                         | _    | 50               | V    |

|                                                         |                       | SG open circuit                                    | _                         | _    | 8                | mA   |

| V <sub>IN</sub> Quiescent Current                       | I <sub>INS</sub>      | EN = GND                                           | _                         | 4    | 10               | μA   |

| VREG Output Voltage                                     | V <sub>REG</sub>      | I <sub>REG</sub> = 0 to 2 mA                       | 4.75                      | 5    | 5.25             | V    |

| Gate Output Drive                                       |                       | · · · ·                                            |                           |      | II               |      |

| Turn-On Time                                            | t <sub>r</sub>        | C <sub>LOAD</sub> = 1 nF, 20% to 80%               | -                         | 35   | -                | ns   |

| Turn-Off Time                                           | t <sub>f</sub>        | C <sub>LOAD</sub> = 1 nF, 80% to 20%               | -                         | 35   | _                | ns   |

| Maximum Duty Cycle                                      | D                     | t <sub>on</sub> × f <sub>osc</sub>                 | 80                        | 85   | _                | %    |

| Dull Ha On Desistance                                   |                       | T <sub>J</sub> = 25°C, I <sub>GHx</sub> = -100 mA  | _                         | 1.7  | _                | Ω    |

| Pull-Up On Resistance                                   | R <sub>DS(on)UP</sub> | T <sub>J</sub> = 150°C, I <sub>GHx</sub> = –100 mA | -                         | _    | 3.5              | Ω    |

|                                                         | 5                     | T <sub>J</sub> = 25°C, I <sub>GLx</sub> = 100 mA   | -                         | 1    | _                | Ω    |

| Pull-Down On Resistance                                 | R <sub>DS(on)DN</sub> | T <sub>J</sub> = 150°C, I <sub>GLx</sub> = 100 mA  | -                         | _    | 2                | Ω    |

| Output High Voltage                                     | V <sub>SGH</sub>      | I <sub>SG</sub> = -100 μA                          | V <sub>REG</sub> –<br>0.1 | _    | V <sub>REG</sub> | V    |

| Output Low Voltage V <sub>SGL</sub>                     |                       | I <sub>SG</sub> = 100 μA                           | _                         | _    | 0.1              | V    |

| Logic Inputs and Outputs                                |                       |                                                    |                           |      | II               |      |

| Fault Output (Open Drain)                               | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA, fault not asserted         | -                         | _    | 0.4              | V    |

| Fault Output FF1 Sink Current <sup>1</sup>              | I <sub>OH(snk)</sub>  | 0.4 V < V <sub>O</sub> < 50 V, fault not asserted  | -                         | 1.3  | _                | mA   |

| Fault Output FF1 Leakage Current <sup>1</sup>           | I <sub>OH1(lkg)</sub> | V <sub>O</sub> = 12 V, fault asserted              | -1                        | _    | 1                | μA   |

| Fault Output FF2 Leakage Current <sup>1</sup>           | I <sub>OH2(lkg)</sub> | V <sub>O</sub> = 5 V, fault asserted               | -5                        | _    | 5                | μA   |

| Input Low Voltage                                       | V <sub>IL</sub>       |                                                    | -                         | _    | 0.8              | V    |

| Input High Voltage                                      | V <sub>IH</sub>       |                                                    | 2                         | _    | _                | V    |

| Input Hysteresis                                        | V <sub>lhys</sub>     |                                                    | 225                       | 330  | _                | mV   |

| Enable Input Internal Clamp Voltage                     | V <sub>ENC</sub>      |                                                    | -                         | 8.4  | _                | V    |

| Enable Input Current Limit Resistor                     | R <sub>EN</sub>       | Between EN and internal clamp                      | -                         | 200  | -                | kΩ   |

| Disable Time                                            | t <sub>DIS</sub>      | f <sub>OSC</sub> = 350 kHz                         | -                         | 94   | -                | ms   |

| Oscillator                                              |                       | ·                                                  |                           |      |                  |      |

|                                                         |                       | $R_{OSC} = 43 \text{ k}\Omega$                     | -                         | 500  | _                | kHz  |

| Oscillator Frequency                                    | f <sub>OSC</sub>      | $R_{OSC} = 62 \text{ k}\Omega$                     | 315                       | 350  | 385              | kHz  |

|                                                         |                       | R <sub>OSC</sub> = V <sub>REG</sub>                | -                         | 350  | _                | kHz  |

| OSC Pin Voltage                                         | V <sub>OSC</sub>      | R <sub>OSC</sub> = 62 kΩ                           | 1.15                      | 1.2  | 1.25             | V    |

| CKOUT Output Delay                                      | t <sub>DC</sub>       | OSC input rise to CKOUT rise                       | -                         | 150  | _                | ns   |

| OSC Input Low Voltage                                   | V <sub>OIL</sub>      |                                                    | -                         | _    | 0.8              | V    |

| OSC Input High Voltage                                  | V <sub>OIH</sub>      |                                                    | 3.5                       | _    | -                | V    |

| OSC Input Hysteresis                                    | V <sub>Oihys</sub>    |                                                    | 300                       | 600  | _                | mV   |

Continued on the next page...

#### **ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued) Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{IN} = 6$ to 40 V; unless otherwise noted

| Characteristics Symbo                            |                       | Test Conditions                                      | Min.                 | Тур. | Max.             | Unit |

|--------------------------------------------------|-----------------------|------------------------------------------------------|----------------------|------|------------------|------|

| Oscillator (continued)                           |                       |                                                      | · · · ·              |      |                  |      |

| OSC Watchdog Period t <sub>OSWD</sub>            |                       | Between successive rising edges                      | 7                    | _    | _                | μs   |

| CKOUT Output High Voltage                        | V <sub>COH</sub>      | I <sub>OH</sub> = -1 mA                              | V <sub>REG</sub> – 1 | _    | V <sub>REG</sub> | V    |

| CKOUT Output Low Voltage                         | V <sub>COL</sub>      | I <sub>OL</sub> = 1 mA                               | -                    | _    | 0.4              | V    |

| LED Current Sense                                |                       |                                                      |                      |      |                  |      |

| Input Bias Current LN                            | I <sub>LN</sub>       | LP = LN = 0 V                                        | -                    | -2   | -                | μA   |

| Input Bias Current LP                            | I <sub>LP</sub>       | LP = LN = 0 V                                        | _                    | -25  | -                | μA   |

| Differential Input Voltage (Active)              | V <sub>IDL</sub>      | $EN = High, V_{IDL} = V_{LP} - V_{LN}$               | _                    | 100  | -                | mV   |

| Differential Input Voltage (PWM off)             | V <sub>IDLO</sub>     | $EN = Low, V_{IDL} = V_{LP} - V_{LN}$                | _                    | 8    | -                | mV   |

| Input Common-Mode Range                          | V <sub>CMLL</sub>     | $V_{LP} = V_{LN}$                                    | 0                    | _    | 1                | V    |

| Current Error                                    | E <sub>ISL</sub>      | $[(10 \times I_{LED} \times R_{SL}) - 1] \times 100$ | -5                   | _    | 5                | %    |

| Switch Current Sense                             |                       |                                                      |                      |      |                  |      |

| Input Bias Current                               | I <sub>BIASS</sub>    | SP = SN = 0 to 2 V                                   | -30                  | _    | -                | μA   |

| Maximum Differential Input Voltage <sup>3</sup>  | V <sub>IDS</sub>      | $V_{IDS} = V_{SP} - V_{SN}$ with D = 50%             | 330                  | 410  | 490              | mV   |

| Input Source Current                             | I <sub>INS</sub>      | V <sub>IDS</sub> = 400 mV                            | _                    | 400  | -                | μA   |

| Input Common-Mode Range                          | V <sub>CMS</sub>      | V <sub>SP</sub> = V <sub>SN</sub>                    | 0                    | _    | 2                | V    |

| Diagnostics and Protection                       |                       |                                                      |                      |      |                  |      |

| Fault Blank Timer <sup>4</sup>                   | t <sub>FB</sub>       | Start-up                                             | -                    | 3    | -                | ms   |

| VREG Undervoltage Turn-Off                       | V <sub>REGUV</sub>    | Decreasing V <sub>REG</sub>                          | 3.3                  | 3.8  | 4.0              | V    |

| VREG Undervoltage Hysteresis                     | V <sub>REGUVhys</sub> |                                                      | 100                  | 120  | -                | mV   |

| LED String Short Voltage                         | V <sub>SCL</sub>      |                                                      | 430                  | 505  | 580              | mV   |

| Non-Reference LED Short Offset<br>Voltage        | V <sub>sco</sub>      |                                                      | 160                  | 200  | 240              | mV   |

| Reference LED Short Offset Voltage               | V <sub>SCOR</sub>     |                                                      | 430                  | 505  | 580              | mV   |

| LED Open Voltage                                 | V <sub>OCL</sub>      |                                                      | 5                    | 5.5  | 6                | V    |

| LF Bias Current                                  | I <sub>LF</sub>       | LF = 1.7 V                                           | -                    | 8    | -                | μA   |

| LA Bias Current                                  | I <sub>LA</sub>       | LA = 1.7 V                                           | -                    | 34   | -                | μA   |

| LED Undercurrent Voltage Difference <sup>5</sup> | V <sub>UCL</sub>      | V <sub>UCL</sub> –                                   |                      | 1    | _                | mV   |

| Open Fault Time-Out                              | t <sub>OTO</sub>      | f <sub>OSC</sub> = 350 kHz                           | -                    | 94   | _                | ms   |

| Overtemperature Warning Threshold                | T <sub>JF</sub>       | Temperature increasing                               | _                    | 170  | _                | °C   |

| Overtemperature Hysteresis                       | T <sub>Jhys</sub>     | Recovery = T <sub>JF</sub> – T <sub>Jhys</sub>       | _                    | 15   | _                | °C   |

<sup>1</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

<sup>2</sup>Function is correct but parameters are not guaranteed below the general limit (6 V).

<sup>3</sup>Parameters guaranteed by design.

<sup>4</sup>Fault Blank timer not enabled for open-LED condition.

<sup>5</sup>Undercurrent when V<sub>SENSEL</sub> < V<sub>IDL</sub> – V<sub>UCL</sub>, where V<sub>SENSEL</sub> is the voltage across the LED current sense resistor R<sub>SL</sub>.

#### **Functional Description**

The A6266 is a boost converter controller that is designed to drive series-connected high power LEDs in automotive applications. It provides programmable constant current output at load voltages and currents limited only by the external components. For automotive applications optimum performance is achieved when driving up to 15 LEDs at currents up to 1 A.

The A6266 integrates all necessary control elements to provide a cost-effective solution using a single external logic-level MOSFET and minimum additional external passive components.

The LED current is set by selecting an appropriate value for the sense resistor value and using the EN input to provide simple on-off control or for PWM brightness control using a suitable externally generated PWM signal. The LED current can be reduced in a single step by reducing the voltage between the IREF pin and GND to less than 1 V.

The pin functions and circuit operation are described in detail in the following sections.

#### **Pin Functions**

**VIN** Supply to the control circuit. A bypass capacitor must be connected between this pin and GND.

**GND** Ground reference connection. This pin should be connected directly to the negative supply.

**EN** Logic input to enable operation. Can be used as direct PWM input. Chip enters low power sleep mode when low for longer than the disable time, t<sub>DIS</sub>.

**FF1** Fault Flag output and isolation control. Open drain current sink output, when high impedance indicates detection of a critical circuit fault. An external pull-up resistor should be connected to a suitable logic supply for simple logic fault flag operation or to the source of the PMOS FET used to isolate the load from the supply. Table 1 defines when FF1 is active. If FF1 is pulled low when an output short fault is indicated then the output disable will be overridden.

FF2 Fault Flag output. Open drain output, when high impedance

indicates detection of a circuit fault. An external pull-up resistor should be connected to a suitable logic supply. If VREG is not used, then the logic supply should not be pulled 300 mV above VREG. Table 1 defines when FF2 is active. If FF2 is pulled low when an open LED fault is indicated then the output disable will be overridden.

**OSC** Resistor to ground to set the internal oscillator or clock input from external oscillator. When connected to VREG the oscillator runs at typically 350 kHz. Higher accuracy in the frequency is possible by connecting a resistor from this pin to ground or by driving this pin with an external precision oscillator.

**CKOUT** Logic output at the oscillator frequency with phase shift. Used to drive succeeding controllers to interleave switching instants.

**IREF** LED current reference modifier. A voltage input that can be used to reduce the LED current sense voltage. When connected to VREG, the current sense voltage,  $V_{IDL}$ , and the value of the sense resistor,  $R_{SL}$ , define the maximum LED current.

**SG** Gate drive for external logic-level MOSFET low-side switch that connects the inductor to ground.

**SP, SN** Sense amplifier connections for switch current limit sense resistor,  $R_{SS}$ .

**LP** Positive sense amplifier connection for LED current limit sense resistor,  $R_{SL}$ . This pin is also the bias supply for the LED current sense amplifier.

${\sf LN}$  Negative sense amplifier connection for LED current limit sense resistor,  ${\sf R}_{\rm SL}.$

VREG Compensation capacitor for internal 5 V regulator.

**LA** Anode reference connection to LEDs. Using an external resistor divider with the same ratio as the number of LEDs provides a measurement of the voltage across all LEDs in the load. This is compared to the voltage on the LF pin to provide shorted LED detection. In addition, it is compared against voltage references to provide open circuit or shorted LED string detection.

**LF** Single diode forward voltage reference input. Measures the forward voltage of the first LED. This value is used as a reference against the voltage on the LA pin to detect possible shorted LEDs in the LED string.

#### **Circuit Operation**

**Converter** A constant frequency, current mode control scheme is used to regulate the current through the LEDs. There are two control loops within the regulator. The inner loop formed by the amplifier, AS (see the Functional Block Diagram for AS, AC, AE, and AL), comparator, AC, and the RS bistable, controls the inductor current as measured through the switch by the switch sense resistor,  $R_{SS}$ .

The outer loop including the amplifier, AL, and the integrating error amplifier, AE, controls the average LED current by providing a setpoint reference for the inner loop.

The LED current is measured by the LED sense resistor,  $R_{SL}$ , and compared to the internal reference current to produce an integrated error signal at the output of AE. This error signal sets the average amount of energy required from the inductor by the LEDs. The average inductor energy transferred to the LEDs is defined by the average inductor current as determined by the inner control loop.

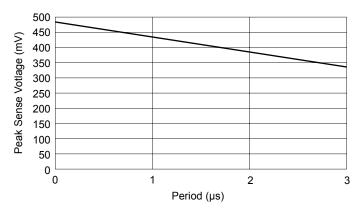

The inner loop establishes the average inductor current by controlling the peak switch current on a cycle-by-cycle basis. Because the relationship between peak current and average current is non-linear, depending on the duty cycle, the reference level for the peak switch current is modified by a slope generator. This compensation reduces the peak switch current measurement by a small amount as the duty cycle increases (refer to figure 1). The slope compensation also removes the instability inherent in a fixed frequency current control scheme.

The control loops work together as follows: the switch current, sensed by the switch current sense resistor,  $R_{SS}$ , is compared to the LED current error signal. As the LED current increases the output of AE will reduce, reducing the peak switch current and thus the current delivered to the LEDs. As the LED current decreases the output of AE increases, increasing the peak switch current and thus increasing the current delivered to the LEDs.

Under some conditions, especially when the LED current is set to a low value, the energy required in the inductor may result in the inductor current dropping to zero for part of each cycle. This is known as discontinuous mode operation, and results in some low frequency ripple. The average LED current, however, remains regulated down to zero. In discontinuous mode, when the inductor current drops to zero, the voltage at the drain of the external MOSFET rings, due to the resonant LC circuit formed by the inductor, and the switch and diode capacitance. This ringing is low frequency and is not harmful.

**Switch Current Limit** The switch current is measured by the switch sense resistor,  $R_{SS}$ , and the switch sense amplifier, AS (see the Functional Block Diagram). The input limit of the sense amplifier,  $V_{IDS}$ , and the maximum switch current,  $I_{SMAX}$ , define the maximum value of the sense resistor as:

$$R_{\rm SS} = V_{\rm IDS} / I_{\rm SMAX} \tag{1}$$

This defines the maximum measurable value of the switch (and inductor) current.

The maximum switch current is modulated by the on-time of the switch. An internal slope compensation signal is subtracted from the voltage sense signal to produce a peak sense voltage which effectively defines the current limit. This signal is applied at a rate of  $-50 \text{ mV}/\mu\text{s}$  starting with no contribution (t=0 µs) at the beginning of each switching cycle. Figure 1 illustrates how the peak sense voltage (typical values) changes over a period of 3 µs.

For example, the maximum current (typical) through the switch at t = 1.5  $\mu$ s (D=50%) would be 410 mV/R<sub>SS</sub>, however, if the switch remained on for a further 1  $\mu$ s, the maximum current through the switch would be 360 mV/R<sub>SS</sub>.

Figure 1. Slope compensation for peak switch current control.

**LED Current Level** The LED current is determined by a combination of the LED sense resistor,  $R_{SL}$ , the LED current threshold voltage,  $V_{IDL}$ , and the voltage between the IREF pin and GND ( $V_{IREF}$ ).

The 100% current level, when the IREF pin is connected to VREG, is defined as:

$$I_{\rm LED}(\rm max) = V_{\rm IDL} / R_{\rm SL}$$

(2)

If  $V_{IREF}$  is less than 1 V then the 100% current level is defined as:

$$I_{\text{LED}}(\text{max}) = V_{\text{IREF}} / (10 \times R_{\text{SL}})$$

(3)

This feature provides direct analog dimming using a voltage from 0 to 1 V. This can be used to provide intensity-matching between modules or groups of LEDs in critical display or backlighting applications. It can also be used to provide a soft start, by connecting a capacitor from IREF to GND and a resistor from IREF to VREG, or one-step dimming by use of a single logic control.

**LED Brightness: PWM Dimming** LED brightness can be controlled by changing the current, which affects the light intensity. However in some applications, for example with amber LEDs, this will have some effect on the color of the LEDs. In these cases it is more desirable to control the brightness by switching the fixed LED current with a pulse width modulated signal. This allows the LED brightness to be set with little effect on the LED color and intensity and allows direct digital control of the LED brightness.

A PWM signal can be applied to the EN input to enable PWM dimming. The period of this signal should be less than the minimum disable time,  $t_{DIS}$ . During PWM dimming, the A6266 switches the LED current between 100% and typically 8% of the full current. This ensures that the voltage change across the LED string is limited to a few volts, depending on the number of LEDs. This limits the stress on the load capacitor (across the string of LEDs) due to large changes in voltage. If the load capacitor is a multilayer ceramic type, then this will reduce any audible noise due to the piezoelectric effect of the capacitor.

The rate of change of the LED current is also limited, to reduce any large variations in the input current.

**Sleep Mode** If EN is held low for longer than the disable time,  $t_{DIS}$ , then the A6266 will shut down and put all sections into a low-power sleep mode. In this mode the bias current is typically less than 4  $\mu$ A.

Note that the disable time is derived from the oscillator period by a ratio of 32,768, so any variation in the oscillator frequency will change the disable time.

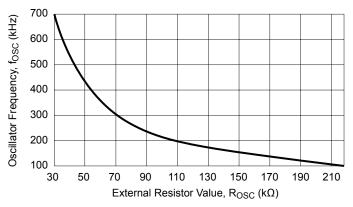

**Oscillator** The main oscillator may be configured as a clock source or it may be driven by an external clock signal. The oscillator is designed to run between 100 and 700 kHz.

When the oscillator is configured as a clock source, the frequency is controlled by a single external resistor,  $R_{OSC}$  (k $\Omega$ ), between the OSC pin and the GND pin. The oscillator frequency is approximately:

$$f_{\rm OSC} = 21700 / R_{\rm OSC} \quad (\rm kHz) \tag{4}$$

Figure 2 shows the resulting  $f_{OSC}$  for various values of  $R_{OSC}$ . If the OSC pin is connected to VREG or GND, the oscillator frequency will be set internally to approximately 350 kHz.

When an external clock source is used to drive the OSC pin, it can synchronize a number of A6266s operating together. This ensures that only a single fundamental frequency is detectable on the supply line, thus simplifying the design of any required EMC filter. The disadvantage of using a single external clock source is that all controllers will be switching current from the supply at the same time. However, this effect may be reduced, and the EMC performance may be further enhanced, by using the CKOUT pin of another A6266 as the external clock source. In this case the switching point of each subsequent A6266 in the chain will be delayed from that of the previous A6266, and the current pulses will be spread across the oscillator period.

Figure 2. Internal oscillator frequency when set by ROSC

#### Diagnostics

The circuit includes several diagnostic and safety functions to assist in ensuring safe operation of the LEDs, the A6266, and the external components. When any fault is detected, one or both of the fault flag outputs, FF1 and FF2, will be inactive (high impedance, open drain) until the fault is removed. The action taken by the A6266 when a fault occurs is defined in table 1. To be able to monitor the state of FF1 and FF2, add a suitable external pull-up resistor.

The A6266 will continue to drive the LEDs under most fault conditions and will only disable the drive to the LEDs when a high voltage hazard is present or the external components are likely to be over-stressed. For output short circuits or open LED conditions, the fault status is latched until EN is taken low or a power cycle occurs. For output short circuits or a shorted LED string, the fault status is latched until either EN is taken low for a period greater than the disable time, or a power cycle occurs.

At start-up, a Fault Blank period,  $t_{FB}$ , occurs before the fault detection circuitry becomes active. This period allows steady state conditions to be established before fault monitoring takes place.

Note that no fault blanking is applied to open LED faults. This is generally not an issue because the charging of the output filter capacitor provides a degree of filtering. In addition, extremely high voltages are prevented from causing potential device breakdown, for example in the external switching MOSFET.

**VREG Undervoltage** If the voltage at VREG,  $V_{REG}$ , drops below the specified turnoff voltage,  $V_{REGUV}$ , the gate drive

#### Table 1. Fault Table

| Fault              | P   | in  | Action    | Latched |

|--------------------|-----|-----|-----------|---------|

| Fault              | FF1 | FF2 | Action    | Latcheu |

| No Fault           | L   | L   | No Action | -       |

| VREG Undervoltage  | Z   | Z   | Disable*  | No      |

| Output Short       | Z   | L   | Disable*  | Yes     |

| LED Undercurrent   | L   | Z   | No Action | No      |

| Overtemperature    | L   | Z   | No Action | No      |

| Open LED           | L   | Z   | Disable*  | Yes     |

| Shorted LED        | L   | Z   | No Action | No      |

| Shorted LED String | Z   | L   | Disable*  | Yes     |

\* SG low, MOSFET off

L = active pull-down, Z = inactive, open drain

output, SG, will be driven low and both fault flags, FF1 and FF2, will be high impedance.  $V_{REG}$  must rise above the turn-on threshold,  $V_{REGUV} + \Delta V_{REGUV}$ , before the output circuits are activated. This ensures that the external FET is operating in its fully enhanced state and avoids permanent damage to the FET, caused by overheating.

**LED Undercurrent** Under some circuit conditions, particularly during a low input voltage condition, it is possible that there could be insufficient drive to maintain the current to the LEDs at the required level. If the voltage across the LED current sense resistor,  $R_{SS}$ , falls below the target sense voltage,  $V_{IDL}$ , by an amount that is more than the LED undercurrent voltage difference,  $V_{UCL}$ , the A6266 will indicate an LED undercurrent condition by setting FF2 to high impedance. However, the A6266 will continue to drive the output. When the output again reaches the required current level, FF2 will go low.

**Overtemperature Warning** If the chip temperature exceeds the overtemperature threshold,  $T_{JF}$ , fault flag FF2 will be high impedance. No action will be taken by the A6266 to limit the chip temperature. An external control circuit must take action to avoid permanent damage to the A6266 and/or the LEDs. The temperature will continue to be monitored and the fault flags will be deactivated when the temperature drops below the recovery threshold provided by the hysteresis,  $T_{Jhys}$ .

**LED Diagnostics** The status of the LEDs in the load can be determined by monitoring the voltage with respect to ground at the three pins LP, LF, and LA, namely  $V_{LP}$ ,  $V_{LF}$ , and  $V_{LA}$ . These voltages provide two differential voltage measurements:

• the voltage across a single reference LED:

$$V_{\rm LED} = V_{\rm LF} - V_{\rm LP} \tag{5}$$

• the ratio of the voltage across all LEDs in a single string:

$$V_{\rm STR} = V_{\rm LA} - V_{\rm LP} \tag{6}$$

The voltage,  $V_{STR}$ , is derived from the voltage across all LEDs in the string, by an external resistor divider with a ratio equal to the quantity of LEDs in the string. To minimize the effects of the bias currents introducing an offset voltage, it is recommended that the resistor between LP and LA should be approximately 560  $\Omega$ .

So for example, if eight LEDs were used, the ratio required would be an eighth, therefore the resistor connected between LA and the anode end of the LED string would be  $3.9 \text{ k}\Omega$ ; 560/[560 + 3900] = 1/8.

These measurements are used to determine if there is an open circuit, if one or more LEDs are shorted, if the output is shorted, or if there is a short across the LED string. Each condition is described in turn in the following sections.

**Open LED**–An open circuit is evaluated when:

$$V_{\rm STR} > V_{\rm OCL} \tag{7}$$

where  $V_{OCL}$  is the LED open circuit voltage defined in the Electrical Characteristics table.

Because the output is current-controlled it is possible for an open circuit on the output to cause extremely high voltages to be present. Therefore, to prevent any hazardous voltages or damage to the circuits, the gate drive output, SG, is immediately driven low when an open circuit is detected. After an open circuit fault has been detected, FF2 will become high impedance, and the open circuit fault state will remain until the open fault time-out period toto, expires. When the gate drive output is re-enabled at the end of the open circuit. If the open circuit is still present, then the fault will again be flagged and the switch drive disabled. This cycle will continue, as long as the open circuit condition is present.

Note that the Fault Blank timer is not used when an open LED fault occurs. This is to avoid potentially damaging voltages appearing in the power circuitry.

**Shorted LED** – A short circuit on one or more LEDs is detected when:

• for the first (reference) LED:

$$V_{\rm STR} > V_{\rm LED} + V_{\rm SCOR}$$

(8)

• for other than the first (reference) LED:

$$V_{\rm LED} > V_{\rm STR} + V_{\rm SCO} \tag{9}$$

where  $V_{STR}$  and  $V_{LED}$  are as defined above,  $V_{SCO}$  is the nonreference LED short offset voltage, and  $V_{SCOR}$  is the reference LED short offset voltage.  $V_{SCO}$  and  $V_{SCOR}$  are defined in the Electrical Characteristics table.

When a short is present, the fault flag FF2 is high impedance, but the regulator continues to operate and drives the remaining LEDs with the correct regulated current. FF2 will remain high impedance while the short circuit condition is present.

A short circuit on one or more LEDs will not cause a hazard because the output is current-controlled. If one LED fails and

becomes a short circuit, then the remaining LEDs will continue to be lit with the same current through, and voltage across, each LED.

Note—Accuracy: The output status monitor relies on all the LEDs in the load having a similar forward voltage drop. Where possible all the LEDs forming the load for a single controller should be taken from the same voltage bin. With only two or three LEDs a wider variation in forward voltage is acceptable, but the selection of LEDs from the same bin is more critical when higher numbers of LEDs are used in a single string.

**Shorted LED String or Output Short** – A short circuit across the LED string, is detected when:

$$V_{\rm STR} < V_{\rm SCL} \tag{10}$$

An output short can consist of the LP, LN, or LF terminals of the LED string being shorted, either to the battery terminal or to ground. Either a shorted LED string or output short will be latched and will only be cleared by pulling EN low for a period greater than the disable time, or by cycling the power.

If either a shorted LED string, or an output short is detected, the A6266 will stop the switching action by pulling SG low. The fault flag FF1 will go high impedance and should be pulled up to the supply with suitable external pull-up resistors to indicate the fault. Either a shorted LED string or output short will be latched and will only be cleared by pulling EN low for a period greater than the disable time, or by cycling the power.

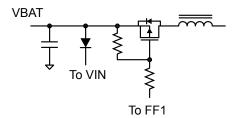

The FF1 output can also be used with pull-up resistors and a P-channel MOSFET in the supply, to isolate the switching elements and the load from the supply. This MOSFET should be connected, as shown in figure 3, with the source connected to the supply and the drain connected to the inductor of the converter.

Figure 3. Example of a supply isolation MOSFET

Two pull-up resistors are used to limit the voltage across the gatesource junction during high input voltages or load dump conditions. If the battery voltage is restricted, one resistor across the gate-source junction can be used. The FF1 provides a sink current of up to 1.3 mA.

This circuit can be used to avoid most hazardous conditions and protect the circuit components from over-stress. Note that under extreme cases, the circuit cannot protect against certain fault conditions. For example, when any of the following occurs:

- If the cathode end of the LED string is shorted to VBAT, the LED sense resistor effectively appears between VBAT and ground. Depending on the current limit of the source supply or the input fuse rating, the fault current may damage the resistor.

- If the LF node is shorted to VBAT, the reference LED and the LED sense resistor effectively appear between VBAT and ground. Depending on the current limit of the source supply or the input fuse rating, the fault current may damage the resistor and/or the reference LED.

- If the cathode end of the LED string is shorted to ground. A fault current determined by the impedance of the shorting link (now effectively the LED sense resistor) flows through the power circuit. The fault current will either: be limited by the maximum switch current sense, V<sub>IDS</sub>, or if the source supply cannot maintain this current, be limited by the source supply. (The source supply will either: fold back, or if the current exceeds the input fuse rating, the fuse will blow, creating an open circuit).

To ensure the A6266 inputs (LP and LN) are not damaged during any of the above faults, it is necessary to add a differential resistor in series with the LN connection (between the sense resistor and the LN pin). This resistor value should be approximately 150  $\Omega$ .

If an output short is detected but it is necessary to keep the output active, the FF1 output can be pulled low. This will override the output disable but will not clear the fault.

#### **Application Information**

#### **Component Selection**

External component selection is critical to the successful application of the LED driver. Although the inductor, the switching MOSFET, and the output capacitor are the most critical elements, the specification of the rectifying diode and sense resistors should also be carefully considered.

The starting point for component selection is to define the maximum LED current, the voltage across the LEDs, and the input operating voltage range. This then allows the average inductor current under worst case conditions to be calculated. The inductor value is then selected based on the acceptable inductor ripple current. The amount of ripple current will then determine the maximum inductor current under worst case conditions. From this current the switch current sense resistor can be calculated.

**LED Current Sense Resistor (R\_{LS})** If the voltage at the IREF pin,  $V_{IREF}$ , is greater than 1V, or if IREF is tied to VREG, then the value of the LED current sense resistor,  $R_{LS}$ , can be calculated from:

$$R_{\rm LS} = V_{\rm IDL} / I_{\rm LED}(\rm max) \tag{11}$$

where  $V_{IDL}$  is the differential voltage across the LED current sense amplifier and  $I_{LED}(max)$  is the maximum LED current.

If  $V_{IREF}$  is less than 1 V, then the value of the LED current sense resistor can be calculated from:

$$R_{\rm LS} = V_{\rm IREF} / (10 \times I_{\rm LED}(\rm{max}))$$

(12)

The typical value for  $V_{IDL}$  is 100 mV. Examples of various sense resistor values are given in table 2.

The power loss in the current sense resistor is worse at the lowest input voltage:

$$P_{\text{LOSS}} = (V_{\text{LED}} / V_{\text{IN}}(\text{min})) \times R_{\text{LS}} \times I^2_{\text{LED}}$$

(13)

The resistors should be of a low inductance construction. Surface mount chip resistors are usually the most suitable, however, axial or radial leaded resistors can be used provided that the lead length is kept to a minimum.

Table 2. Sense Resistor Values

| l <sub>LED</sub> (max)<br>(mA) | R <sub>LS</sub><br>(mΩ) |

|--------------------------------|-------------------------|

| 350                            | 286                     |

| 700                            | 143                     |

| 1000                           | 100                     |

**Inductor Selection** Selecting the correct inductance is a balance between choosing a value that is small enough to help reduce size and cost, but high enough to ensure that the inductor current ripple is kept to an acceptable level. A reasonable target for the ripple current is 20% of the maximum average current.

The maximum average inductor current is approximately:

$$I_{\text{L(av)}}(\text{max}) = I_{\text{LED}}(\text{max}) \times V_{\text{LED}} / V_{\text{IN}}(\text{min})$$

(14)

The inductor current ripple is approximately:

$$I_{\text{LRIP}} = V_{\text{IN}} \times (V_{\text{LED}} - V_{\text{IN}}) / (f_{\text{OSC}} \times L \times V_{\text{LED}}) \quad (15)$$

The inductor value is therefore:

$$L = V_{\rm IN} \times (V_{\rm LED} - V_{\rm IN}) / (f_{\rm OSC} \times I_{\rm LRIP} \times V_{\rm LED}) \quad (16)$$

where:

V<sub>LED</sub> is the voltage across the LED string,

$V_{IN}$  is the supply voltage,  $V_{IN}(min)$  is the minimum supply voltage, L is the inductor value, and

$f_{OSC}$  is the oscillator frequency.

With an internal oscillator frequency of 350 kHz, the value of the inductor for most cases will be between 20 and 50  $\mu$ H. The maximum inductor current can then be calculated as:

$$I_{L(PK)} = I_{L(av)}(max) + (I_{RIP} / 2)$$

(17)

This defines the minimum peak switch current as set by the switch current sense resistor.

The current rating for the inductor should be greater, by some margin, than the peak value above,  $I_{L(PK)}$ . When selecting an inductor from manufacturers datasheets, there are two current levels usually defined, the smallest value being the figure to work with:

- $\bullet$  Saturation level, where the inductance value typically drops by 10%, or

- Temperature rise, where the part experiences a certain rise in temperature at full rated current. This parameter can be defined between a 20°C and 50°C rise in temperature. It is important to understand how manufacturers define the maximum operating temperature, because this can often incorporate the self-heating temperature rise.

In most cases the limiting current is usually the saturation value. To improve efficiency, the inductor should also have low winding resistance, typically  $< 50 \text{ m}\Omega$ , and the core material will usually be ferrite, with low losses at the oscillator frequency.

Recommended inductor manufacturers/series are:

- Coilcraft/ MSS1278T

- TDK/ SLF12575 type H

**Diode** The diode should have a low forward voltage, to reduce conduction losses, and a low capacitance, to reduce switching losses. Schottky diodes can provide both these features if carefully selected. The forward voltage drop is a natural advantage for Schottky diodes and reduces as the current rating increases. However, as the current rating increases, the diode capacitance also increases so the optimum selection is usually the lowest current rating above the required maximum, in this case  $I_{L(PK)}$ .

**Switch Current Sense Resistor (RSS)** Neither the absolute value of the switch current nor the accuracy of the measurement is important, because the regulator will continuously adjust the switch current, within a closed loop, to provide sufficient energy for the output. For maximum accuracy the switch sense resistor value should be chosen to maximize the differential signal seen by the sense amplifier. The input limit of the sense amplifier,  $V_{IDS}$ , and the maximum switch current,  $I_S(max)$ , therefore define the maximum value of the sense resistor as:

$$R_{\rm SS} = V_{\rm IDS} / I_{\rm S}(\rm max) \tag{18}$$

Where  $I_{S}(max)$  is the maximum switch current and should be set above the maximum inductor current,  $I_{L(PK)}$ .

This represents the maximum measurable value of the switch (and inductor) current; however, the peak switch current will always be less than this, set by the control circuit, depending on the input voltage and the required load conditions. Because the switch current control is within a closed loop, it is possible to reduce the value of the sense resistor to reduce its power dissipation. However this will reduce the accuracy of the regulated LED current.

The power loss in the switch sense resistor is worse at the lowest input voltage:

$$P_{\text{LOSS}} = (V_{\text{LED}} [V_{\text{LED}} - V_{\text{IN}}(\text{min})] / V_{\text{IN}}(\text{min})^2) \times R_{\text{SS}} \times I^2_{\text{LED}}$$

(19)

**External Switch MOSFET** A logic-level N-channel MOSFET is used as the switch for the DC-to-DC converter. The voltage at the drain of the MOSFET is equal to the maximum voltage across the string of LEDs.

The peak switch current is defined by the maximum inductor current,  $I_{L(PK)}$ . However in most cases the MOSFET will be chosen by selecting low on-resistance, which usually results in a current rating of several times the required peak current.

In addition to minimizing cost, the choice of MOSFET should consider both the on-resistance and the total gate charge. The total gate charge will determine the average current required from the internal regulator and thus the power dissipation.

**Output Capacitor** There are several points to consider when selecting the output capacitor.

Unlike some switch-mode regulators, the value of the output capacitor in this case is not critical for output stability. The capacitor value is only limited by the required maximum ripple voltage.

Due to the switching topology used, the ripple current for this circuit is high because the output capacitor provides the LED current when the switch is active. The capacitor is then recharged each time the inductor passes energy to the output. The ripple current on the output capacitor will be equal to the peak inductor current.

Normally this large ripple current, in conjunction with the requirement for a larger capacitance value for stability, would dictate the use of large electrolytic capacitors. However in this case stability is not a consideration, and the capacitor value can be low, allowing the use of ceramic capacitors.

To minimize self-heating effects and voltage ripple, the equivalent series resistance (ESR), and the equivalent series inductance (ESL) should be kept as low as possible. This can be achieved by multilayer ceramic chip (MLCC) capacitors. To reduce performance variation over temperature, low drift types such as X7R and X5R should be used.

The value of the output capacitor will typically be about 10  $\mu F$  and it should be rated above the maximum voltage defined by the series output LEDs.

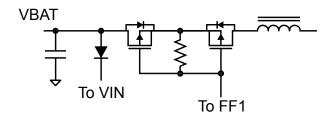

**Reverse Supply Protection** Protection for the A6266 is provided by an external low current diode between the supply and the VIN pin, as shown in the Functional Block Diagram section. The isolation MOSFET shown in figure 3 is only able to provide isolation when the supply polarity is correct. However, with an additional P-channel MOSFET, it is also possible to provide reverse battery protection to the switching elements and the LEDs. The additional FET should be connected, as shown in figure 4, with the drain to the supply and the source to the source connection of the original isolation MOSFET.

In the complete circuit, consideration should be given to limiting the maximum gate-source voltage of the FET. If the supply voltage is likely to exceed 20 V, then either: a Zener clamp must be added in parallel with the gate-source resistor to prevent damage to the FET, or a second resistor added as shown in figure 3.

Figure 4. Example of a supply isolation MOSFET

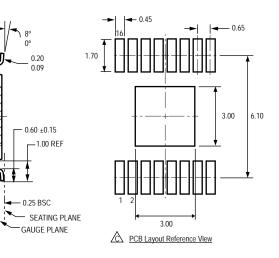

#### Package LP 16-Pin TSSOP with Exposed Thermal Pad

For Reference Only; not for tooling use (reference MO-153 ABT) Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (bottom surface); dimensions may vary with device

Reference land pattern layout (reference IPC7351 SOP65P640X110-17M);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

#### **Revision History**

| Revision | Revision Date    | Description of Revision                   |  |

|----------|------------------|-------------------------------------------|--|

| Rev. 1   | October 11, 2011 | Update diagnostic and protection sections |  |

|          |                  |                                           |  |

Copyright ©2011, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com